供需失衡下的挑戰(zhàn) 2025-2026年中國(guó)EVA市場(chǎng)前瞻分析

作為廣泛應(yīng)用于光伏膠膜、發(fā)泡材料、電線電纜等領(lǐng)域的核心化工原材料,乙烯-醋酸乙烯酯共聚物(EVA)的市場(chǎng)走勢(shì)與宏觀經(jīng)濟(jì)、產(chǎn)業(yè)政策及下游需求緊密相連。綜合當(dāng)前行業(yè)動(dòng)態(tài)與供需格局分析,未來(lái)兩年,中國(guó)EVA市場(chǎng)預(yù)計(jì)將經(jīng)歷一段震蕩調(diào)整期,面臨供應(yīng)加劇而需求增長(zhǎng)乏力的挑戰(zhàn)。

一、 2025年:市場(chǎng)在震蕩中尋求新的平衡點(diǎn)

進(jìn)入2025年,國(guó)內(nèi)EVA市場(chǎng)的主基調(diào)預(yù)計(jì)將是“震蕩下行”。這一趨勢(shì)主要由以下幾方面因素驅(qū)動(dòng):

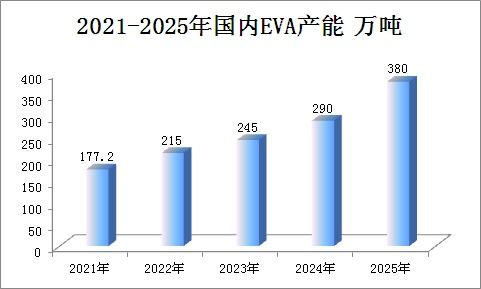

- 供應(yīng)端持續(xù)放量:盡管2025年新增產(chǎn)能投放高峰相較于前兩年有所放緩,但前期已投產(chǎn)裝置的產(chǎn)能將在年內(nèi)得到充分釋放,市場(chǎng)總供應(yīng)量維持在較高水平。部分新進(jìn)入者為搶占市場(chǎng)份額,可能采取靈活的定價(jià)策略,對(duì)市場(chǎng)價(jià)格形成壓力。

- 需求增長(zhǎng)動(dòng)能減弱:作為需求“壓艙石”的光伏行業(yè),其裝機(jī)增速在經(jīng)歷多年高速增長(zhǎng)后,可能逐步回歸理性平穩(wěn)增長(zhǎng)。發(fā)泡鞋材、包裝薄膜等傳統(tǒng)領(lǐng)域需求預(yù)計(jì)保持穩(wěn)定,難有爆發(fā)性增長(zhǎng)亮點(diǎn)。整體需求呈現(xiàn)“穩(wěn)中偏弱”的格局,對(duì)價(jià)格的上行支撐有限。

- 成本與宏觀環(huán)境影響:上游乙烯、醋酸乙烯等原料價(jià)格波動(dòng)及宏觀經(jīng)濟(jì)景氣度,將加劇市場(chǎng)的短期震蕩。下游企業(yè)在采購(gòu)上可能更加謹(jǐn)慎,多維持剛需采購(gòu),難以形成大規(guī)模的集中補(bǔ)庫(kù)需求。

市場(chǎng)將在高供應(yīng)與弱需求的博弈中反復(fù)震蕩,價(jià)格中樞存在下移壓力,行業(yè)利潤(rùn)空間可能被進(jìn)一步壓縮。

二、 2026年:供應(yīng)壓力加劇,行業(yè)競(jìng)爭(zhēng)進(jìn)入深水區(qū)

展望2026年,市場(chǎng)面臨的挑戰(zhàn)或?qū)⒏鼮閲?yán)峻,“供應(yīng)加劇”將成為關(guān)鍵詞。根據(jù)已知的擴(kuò)產(chǎn)計(jì)劃,2026年可能迎來(lái)新一輪的產(chǎn)能集中投放期。大量新增產(chǎn)能的入市,將顯著改變市場(chǎng)的供需結(jié)構(gòu),行業(yè)正式進(jìn)入產(chǎn)能過(guò)剩周期。與此“需求穩(wěn)中偏弱”的態(tài)勢(shì)預(yù)計(jì)將延續(xù),光伏等主要下游領(lǐng)域的增速可能進(jìn)一步放緩。

供需矛盾的尖銳化將導(dǎo)致市場(chǎng)競(jìng)爭(zhēng)白熱化。具有成本、技術(shù)、規(guī)模和下游渠道優(yōu)勢(shì)的一體化龍頭企業(yè),其抗風(fēng)險(xiǎn)能力和市場(chǎng)占有率有望得到鞏固;而部分規(guī)模較小、產(chǎn)品同質(zhì)化嚴(yán)重、成本控制能力弱的企業(yè),則可能面臨巨大的經(jīng)營(yíng)壓力,行業(yè)洗牌與整合進(jìn)程有望加速。

三、 貨物及技術(shù)進(jìn)出口:在變局中探尋新機(jī)遇

在復(fù)雜的國(guó)內(nèi)市場(chǎng)環(huán)境下,進(jìn)出口市場(chǎng)將成為企業(yè)平衡產(chǎn)銷、開拓增長(zhǎng)點(diǎn)的重要途徑。

- 貨物出口:隨著國(guó)內(nèi)產(chǎn)能大幅提升,出口導(dǎo)向?qū)⒏用鞔_。企業(yè)需要積極開拓“一帶一路”沿線國(guó)家及新興市場(chǎng),輸出光伏組件配套用EVA膠膜料、高端鞋材料等優(yōu)勢(shì)產(chǎn)品。也需警惕國(guó)際貿(mào)易環(huán)境變化、反傾銷調(diào)查等潛在風(fēng)險(xiǎn)。

- 技術(shù)進(jìn)口與自主創(chuàng)新:高端EVA產(chǎn)品(如VA含量高、熔指特定的光伏封裝膠膜料)的生產(chǎn)技術(shù)仍存在壁壘。在產(chǎn)能過(guò)剩的大背景下,行業(yè)競(jìng)爭(zhēng)將從“量的擴(kuò)張”轉(zhuǎn)向“質(zhì)的提升”。加大對(duì)高端牌號(hào)、特種牌號(hào)產(chǎn)品的研發(fā)投入,或通過(guò)技術(shù)引進(jìn)、合作開發(fā)等方式突破技術(shù)瓶頸,實(shí)現(xiàn)產(chǎn)品結(jié)構(gòu)的高端化、差異化,是國(guó)內(nèi)企業(yè)提升核心競(jìng)爭(zhēng)力、穿越周期的關(guān)鍵。綠色低碳生產(chǎn)技術(shù)(如溶液法工藝優(yōu)化、生物基原料應(yīng)用等)的引進(jìn)與創(chuàng)新,也將成為未來(lái)發(fā)展的趨勢(shì)。

結(jié)論

2025-2026年中國(guó)EVA市場(chǎng)將步入供應(yīng)主導(dǎo)的調(diào)整階段。企業(yè)需做好應(yīng)對(duì)長(zhǎng)期激烈競(jìng)爭(zhēng)的準(zhǔn)備,主動(dòng)調(diào)整戰(zhàn)略:一方面,通過(guò)技術(shù)與管理創(chuàng)新降本增效,優(yōu)化產(chǎn)品結(jié)構(gòu),向價(jià)值鏈高端攀升;另一方面,積極布局全球市場(chǎng),構(gòu)建國(guó)內(nèi)國(guó)際雙循環(huán)的發(fā)展格局。唯有如此,才能在供需再平衡的過(guò)程中把握主動(dòng)權(quán),實(shí)現(xiàn)可持續(xù)發(fā)展。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.dapeishow.cn/product/73.html

更新時(shí)間:2026-04-14 11:12:31